# 2.65 W Filterless Class-D Audio Amplifier with Integrated Dual SPST Switch

The NLMD5820 is an integrated mono Class-D audio power amplifier and dual SPST switch capable of delivering 2.65 W of continuous average power to 4.0  $\Omega$  from a 5.0 V supply in a Bridge Tied Load (BTL) configuration. Under the same conditions, the output power stage can provide 1.4 W to a 8.0  $\Omega$  BTL load with less than 1% THD+N. For cellular handsets or PDAs it offers space and cost savings because no output filter is required when using inductive tranducers. The NLMD5820 incorporates a dual SPST switch which allows signals to bypass the amplifier. The integrated switch operates off a separate supply voltage and maintains a very low R<sub>ON</sub> resistance, 0.5  $\Omega$  max @ 2.8 V V<sub>CC</sub>.

The NLMD5820 processes analog inputs with a pulse width modulation technique that lowers output noise and THD when compared to a conventional sigma-delta modulator. The device allows independent gain while summing signals from various audio sources. Thus, in cellular handsets, the earpiece, the loudspeaker and even the melody ringer can be driven with a single NLMD5820. Due to its low 42  $\mu$ V noise floor, A-weighted, clean listening is guaranteed no matter the load sensitivity.

#### Features

- Optimized PWM Output Stage: Filterless Capability

- Efficiency up to 90%

Low 2.5 mA Typical Quiescent Current

- Large Output Power Capability: 1.4 W with 8.0  $\Omega$  Load (CSP) and THD + N < 1%

- Dual SPST with 0.5  $\Omega$  Max R<sub>ON</sub> @ V<sub>CC</sub> = 2.8 V

- High Performance, THD+N of 0.03% @  $V_p$  = 5.0 V, R<sub>L</sub> = 8.0  $\Omega$ , P<sub>out</sub> = 100 mW

- Excellent PSRR (-65 dB): No Need for Voltage Regulation

- Surface Mounted Package UDFN16

- Fully Differential Design. Eliminates Two Input Coupling Capacitors

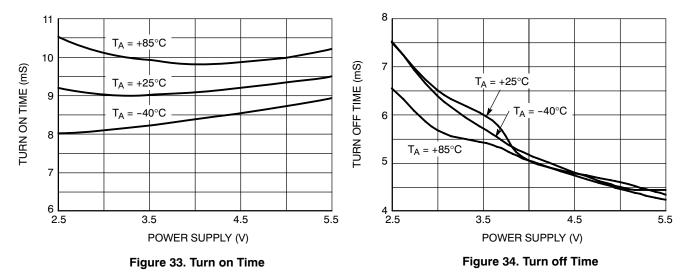

- Very Fast Turn On/Off Times with Advanced Rising and Falling Gain Technique

- External Gain Configuration Capability

- Internally Generated 250 kHz Switching Frequency

- Short Circuit Protection Circuitry

- "Pop and Click" Noise Protection Circuitry

- This is a Pb-Free Device

### Applications

- Cellular Phone

- Portable Electronic Devices

- PDAs and Smart Phones

# **ON Semiconductor®**

http://onsemi.com

A2A = Specific Device Code  $\overline{M}$  = Date Code/Assembly Loc

= Date Code/Assembly Location

= Pb-Free Package

#### **ORDERING INFORMATION**

| Device        | Package                     | Shipping <sup>†</sup> |

|---------------|-----------------------------|-----------------------|

| NLMD5820MUTAG | 16 PIN<br>UDFN<br>(Pb-Free) | 3000/Tape & Reel      |

For

information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specification

Brochure, BRD8011/D.

#### © Semiconductor Components Industries, LLC, 2007 September, 2007 – Rev. 0

| FUNCTION TABLE |         |  |  |  |  |  |

|----------------|---------|--|--|--|--|--|

| IN 1, 2        | NC 1, 2 |  |  |  |  |  |

| 0              | ON      |  |  |  |  |  |

| 1              | OFF     |  |  |  |  |  |

# FUNCTION TARI F

### **PIN DESCRIPTION**

| Pin No. | Symbol          | Туре | Description                                                                                                                                                                                                                       |

|---------|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | NC2             | I/O  | Normally Closed Signal Line for Switch #2.                                                                                                                                                                                        |

| 2       | IN2             | I    | Control Input for Switch #2.                                                                                                                                                                                                      |

| 3       | COM2            | I/O  | Common Signal Line for Switch #2.                                                                                                                                                                                                 |

| 4       | V <sub>CC</sub> | I    | Analog Supply for Switches. Range: 1.65 V – 4.5 V.                                                                                                                                                                                |

| 5       | SD              | I    | The device enters in Shutdown Mode when a low level is applied on this pin. An internal 300 k $\Omega$ resistor will force the device in shutdown mode if no signal is applied to this pin. It also helps to save space and cost. |

| 6       | Vp              | I    | Power Analog Positive Supply. Range: 2.5 V – 5.5 V.                                                                                                                                                                               |

| 7       | INP             | I    | Positive Differential Input.                                                                                                                                                                                                      |

| 8       | INM             | I    | Negative Differential Input.                                                                                                                                                                                                      |

| 9       | OUTP            | 0    | Positive BTL Output.                                                                                                                                                                                                              |

| 10      | Vp              | I    | Analog Positive Supply. Range: 2.5 V - 5.5 V.                                                                                                                                                                                     |

| 11      | GND             | I    | Analog Ground.                                                                                                                                                                                                                    |

| 12      | OUTM            | 0    | Negative BTL Output.                                                                                                                                                                                                              |

| 13      | COM1            | I/O  | Common Signal Line for Switch #1.                                                                                                                                                                                                 |

| 14      | IN1             | I    | Control Input for Switch #1.                                                                                                                                                                                                      |

| 15      | NC1             | I/O  | Normally Closed Signal Line for Switch #1.                                                                                                                                                                                        |

| 16      | GND             | I    | Analog Ground.                                                                                                                                                                                                                    |

#### MAXIMUM RATINGS

| Symbol               | Rating                                                                           |                                            | Мах                                  | Unit |  |

|----------------------|----------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------|------|--|

| Vp                   | Supply Voltage for Amplifier                                                     | Active Mode<br>Shutdown Mode               | 6.0<br>7.0                           | V    |  |

| V <sub>in</sub>      | Input Voltage for Amplifier                                                      |                                            | -0.3 to V <sub>CC</sub> +0.3         | V    |  |

| V <sub>CC</sub>      | Supply Voltage for Switches                                                      |                                            | -0.5 to +5.5                         | V    |  |

| VIS                  | Analog Signal Voltage for Switches ( $V_{NC}$ , or $V_{CO}$                      | ом)                                        | $-0.5 \leq V_{IS} \leq V_{CC} + 0.5$ | V    |  |

| V <sub>IN</sub>      | Control Input for Switches                                                       |                                            | $-0.5 \le V_{\text{IN}} \le +5.5$    | V    |  |

| l <sub>out</sub>     | Max Output Current of Amplifier (Note 1)                                         |                                            | 1.5                                  | А    |  |

| I <sub>anl1</sub>    | Continuous DC Current from COM to NC                                             |                                            | ±300                                 | mA   |  |

| I <sub>anl-pk1</sub> | Peak Current from COM to NC, 10 Duty Cycle                                       | Peak Current from COM to NC, 10 Duty Cycle |                                      | mA   |  |

| I <sub>cImp</sub>    | Continuous DC Current into COM/NC with Resp                                      | pect to V <sub>CC</sub> or GND             | ±100                                 | mA   |  |

| Pd                   | Power Dissipation (Note 2)                                                       |                                            | Internally Limited                   | -    |  |

| TJ                   | Max Junction Temperature                                                         |                                            | 150                                  | °C   |  |

| T <sub>stg</sub>     | Storage Temperature Range                                                        |                                            | -65 to +150                          | °C   |  |

| $R_{\theta JA}$      | Thermal Resistance Junction-to-Air                                               | UDFN16                                     | 50                                   | °C/W |  |

| -<br>-               | ESD Protection<br>Human Body Model (HBM) (Note 3)<br>Machine Model (MM) (Note 4) |                                            | > 2000<br>> 200                      | V    |  |

| -                    | Latchup Current @ $T_A = 85^{\circ}C$ (Note 5)                                   | UDFN16                                     | ±100                                 | mA   |  |

| MSL                  | Moisture Sensitivity (Note 6)                                                    |                                            | Level 1                              |      |  |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. The device is protected by a current breaker structure. See "Current Breaker Circuit" in the Description Information section for more information.

The thermal shutdown is set to 160°C (typical) avoiding irreversible damage to the device due to power dissipation.

Human Body Model: 100 pF discharged through a 1.5 kΩ resistor following specification JESD22/A114.

Machine Model: 200 pF discharged through all pins following specification JESD22/A115.

Latchup Testing per JEDEC Standard JESD78.

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                          | Range                  | Unit |

|-----------------|------------------------------------|------------------------|------|

| VP              | Supply Voltage for Amplifier       | 2.5 to 5.5             | V    |

| V <sub>CC</sub> | Supply Voltage for Switches        | 1.65 to 4.5            | V    |

| V <sub>IS</sub> | Analog Signal Voltage for Switches | GND to V <sub>CC</sub> | V    |

| V <sub>IN</sub> | Control Input for Switches         | GND to V <sub>CC</sub> | V    |

| T <sub>A</sub>  | Operating Ambient Temperature      | -40 to +85             | °C   |

| Characteristic                    | Symbol            | Conditions                                                                                                                               | Min                             | Тур                             | Max                             | Unit   |

|-----------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|--------|

| Supply Quiescent Current          | l <sub>dd</sub>   | $V_p$ = 3.6 V, R <sub>L</sub> = 8.0 $\Omega$<br>$V_p$ = 5.5 V, No Load                                                                   |                                 | 2.15<br>2.61                    | -                               | mA     |

|                                   |                   | $V_{p}$ from 2.5 V to 5.5 V, No Load                                                                                                     |                                 |                                 |                                 |        |

|                                   |                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                            | -                               | -                               | 3.8                             |        |

| Shutdown Current                  | I <sub>sd</sub>   | $V_{p} = 4.2 V$                                                                                                                          |                                 |                                 |                                 | μΑ     |

|                                   |                   | T <sub>A</sub> = +25°C                                                                                                                   | -                               | 0.42<br>0.45                    | 0.8<br>2.0                      |        |

|                                   |                   | $T_{A} = +85^{\circ}C$                                                                                                                   | -                               | 0.45                            | 2.0                             | ^      |

|                                   |                   | V <sub>p</sub> = 5.5 V<br>T <sub>A</sub> = +25°C                                                                                         | _                               | 0.8                             | 1.5                             | μA     |

|                                   |                   | $T_{A} = +25 \text{ G}$<br>$T_{A} = +85^{\circ}\text{C}$                                                                                 | _                               | 0.0                             | -                               |        |

| Shutdown Voltage High             | V <sub>sdih</sub> | _                                                                                                                                        | 1.2                             | -                               | -                               | V      |

| Shutdown Voltage Low              | V <sub>sdil</sub> | _                                                                                                                                        | -                               | -                               | 0.4                             | V      |

| Switching Frequency               | F <sub>sw</sub>   | $V_p$ from 2.5 V to 5.5 V                                                                                                                | 180                             | 240                             | 300                             | kHz    |

|                                   |                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                            |                                 |                                 |                                 |        |

| Gain                              | G                 | R <sub>L</sub> = 8.0 Ω                                                                                                                   | <u>285 kΩ</u><br>R <sub>i</sub> | <u>300 kΩ</u><br>R <sub>i</sub> | <u>315 kΩ</u><br>R <sub>i</sub> | V<br>V |

| Output Impedance in Shutdown Mode | Z <sub>SD</sub>   | _                                                                                                                                        | -                               | 20                              | -                               | kΩ     |

| Resistance from SD to GND         | Rs                | -                                                                                                                                        | -                               | 300                             | -                               | kΩ     |

| Output Offset Voltage             | Vos               | V <sub>p</sub> = 5.5 V                                                                                                                   | -                               | 6.0                             | -                               | mV     |

| Turn On Time                      | Ton               | V <sub>p</sub> from 2.5 V to 5.5 V                                                                                                       | -                               | 1.0                             | -                               | μs     |

| Turn Off Time                     | Toff              | V <sub>p</sub> from 2.5 V to 5.5 V                                                                                                       | -                               | 1.0                             | -                               | μs     |

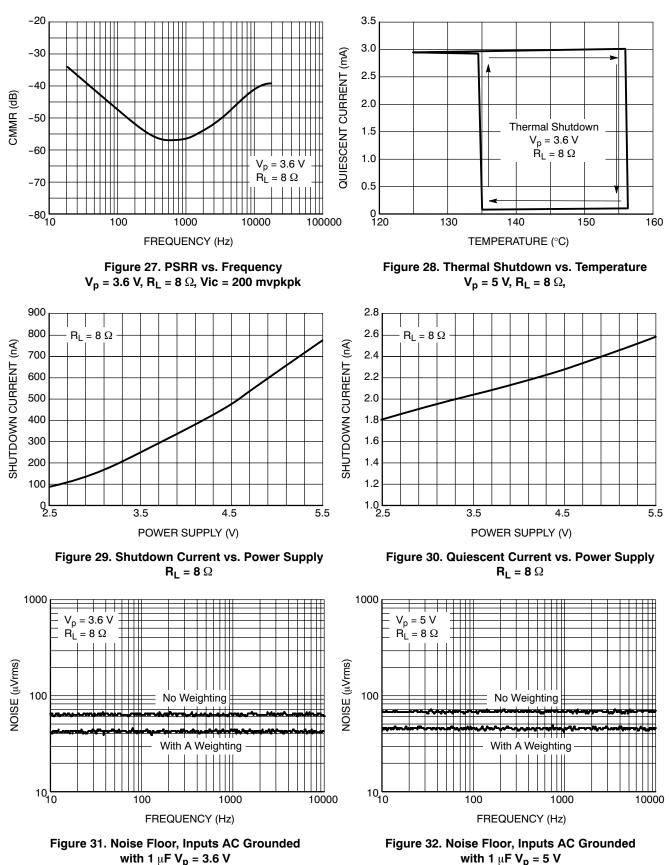

| Thermal Shutdown Temperature      | Tsd               |                                                                                                                                          | -                               | 160                             | -                               | °C     |

| Output Noise Voltage              | Vn                | V <sub>p</sub> = 3.6 V, f = 20 Hz to 20 kHz                                                                                              |                                 |                                 |                                 | μVrms  |

|                                   |                   | no weighting filter                                                                                                                      | -                               | 65                              | -                               |        |

|                                   |                   | with A weighting filter                                                                                                                  | -                               | 42                              | -                               |        |

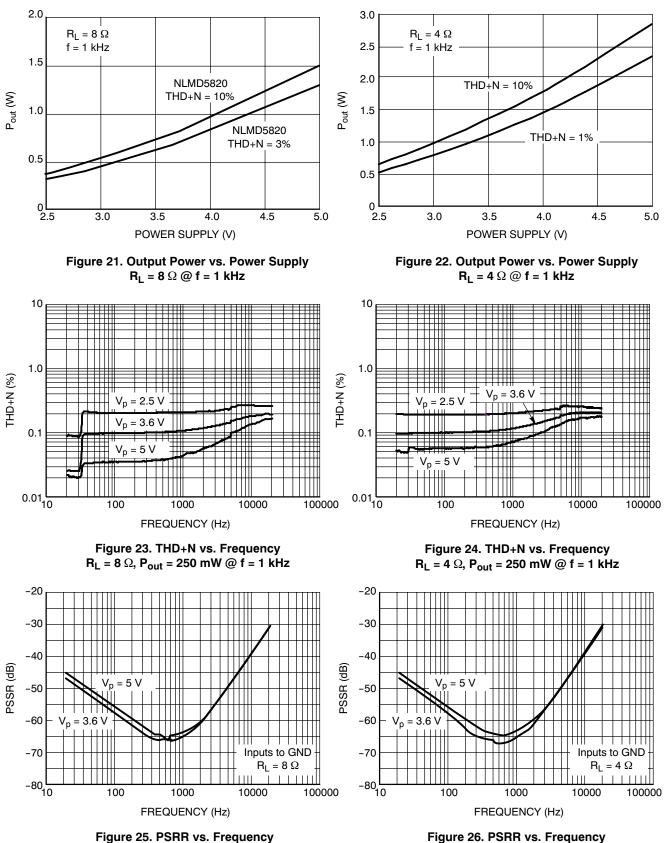

| RMS Output Power                  | Po                | $R_L$ = 8.0 Ω, f = 1.0 kHz, THD+N < 1%                                                                                                   |                                 | 0.22                            |                                 | W      |

|                                   |                   | V <sub>p</sub> = 2.5 V<br>V <sub>p</sub> = 3.0 V                                                                                         | -                               | 0.22                            | _                               |        |

|                                   |                   | $V_{n}^{r} = 3.6 V$                                                                                                                      | -                               | 0.45                            | -                               |        |

|                                   |                   | $V_{p}^{P} = 4.2 V$<br>$V_{p} = 5.0 V$                                                                                                   | -                               | 0.67<br>0.92                    | _                               |        |

|                                   |                   | R <sub>L</sub> = 8.0 Ω, f = 1.0 kHz, THD+N < 10%                                                                                         |                                 |                                 |                                 | w      |

|                                   |                   | V <sub>p</sub> = 2.5 V                                                                                                                   | -                               | 0.36<br>0.53                    | -                               |        |

|                                   |                   | V <sub>p</sub> = 3.0 V<br>V <sub>p</sub> = 3.6 V                                                                                         | _                               | 0.53                            | _                               |        |

|                                   |                   | V <sub>p</sub> <sup>e</sup> = 4.2 V<br>V <sub>p</sub> = 5.0 V                                                                            |                                 | 1.07                            | -                               |        |

|                                   |                   |                                                                                                                                          | -                               | 1.49                            | -                               | W      |

|                                   |                   | R <sub>L</sub> = 4.0 Ω, f = 1.0 kHz, THD+N < 1%<br>$V_p$ = 2.5 V                                                                         | _                               | 0.24                            | -                               | vv     |

|                                   |                   | V <sub>p</sub> <sup>-</sup> = 3.0 V<br>V <sub>p</sub> = 3.6 V                                                                            | -                               | 0.38<br>0.57                    | -                               |        |

|                                   |                   | $V_{p} = 4.2 V$                                                                                                                          | -                               | 0.83                            | -                               |        |

|                                   |                   | $V_{p}^{p} = 5.0 V$                                                                                                                      | -                               | 1.2                             | -                               |        |

|                                   |                   | $R_L$ = 4.0 Ω, f = 1.0 kHz, THD+N < 10%                                                                                                  |                                 | 0.50                            |                                 | W      |

|                                   |                   | V <sub>p</sub> = 2.5 V<br>V <sub>p</sub> = 3.0 V                                                                                         | -                               | 0.52<br>0.8                     | -                               |        |

|                                   |                   | $V_{p} = 3.6 V$                                                                                                                          | -                               | 1.125                           | -                               |        |

|                                   |                   | V <sub>p</sub> <sup>-</sup> = 4.2 V<br>V <sub>p</sub> = 5.0 V                                                                            | -                               | 1.58<br>2.19                    | -                               |        |

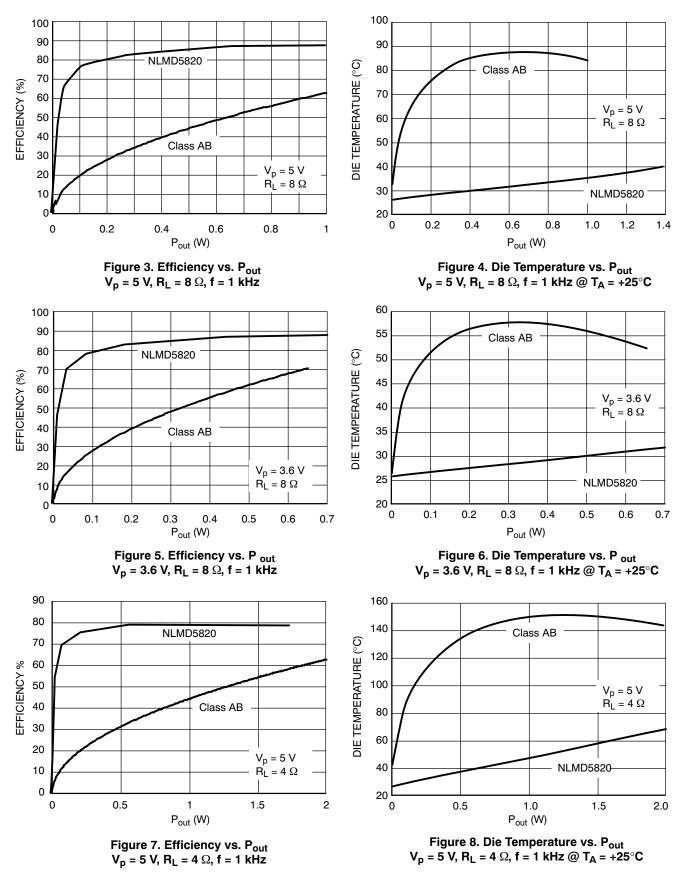

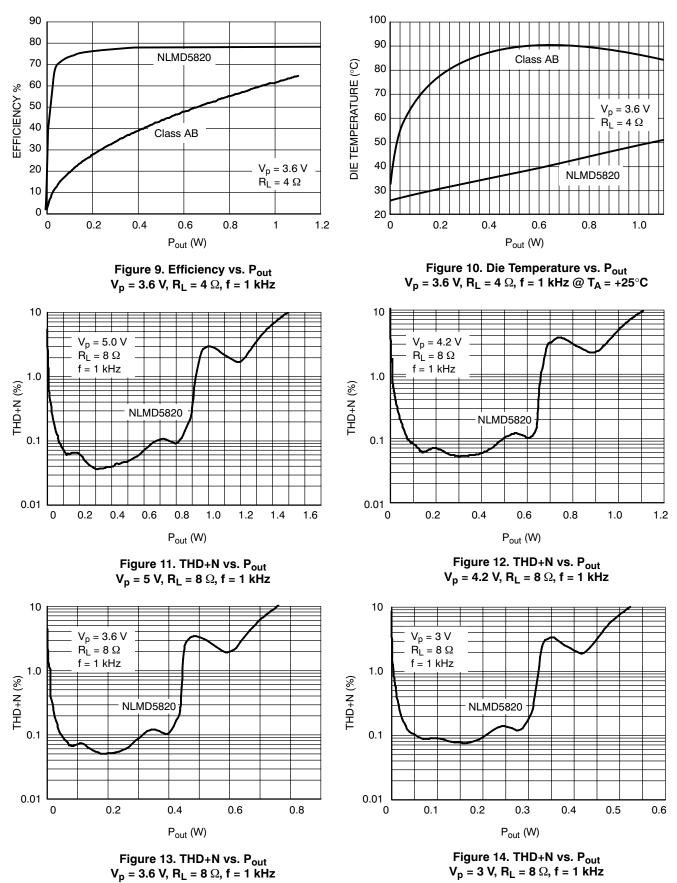

| Efficiency                        | -                 | $R_L$ = 8.0 Ω, f = 1.0 kHz<br>V <sub>p</sub> = 5.0 V, P <sub>out</sub> = 1.2 W<br>V <sub>p</sub> = 3.6 V, P <sub>out</sub> = 0.6 W       |                                 | 87<br>87                        |                                 | %      |

|                                   |                   | $R_L = 4.0 \Omega$ , f = 1.0 kHz<br>V <sub>p</sub> = 5.0 V, P <sub>out</sub> = 2.0 W<br>V <sub>p</sub> = 3.6 V, P <sub>out</sub> = 1.0 W |                                 | 79<br>78                        | -                               |        |

# **ELECTRICAL CHARACTERISTICS OF AMPLIFIER** (Limits apply for $T_A = +25^{\circ}C$ unless otherwise noted)

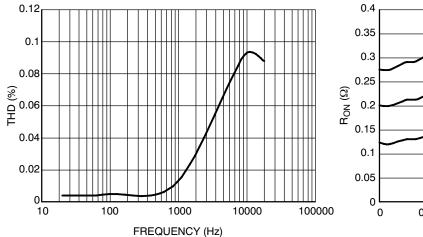

| Characteristic                    | Symbol | Conditions                                                                                | Min | Тур  | Max | Unit |

|-----------------------------------|--------|-------------------------------------------------------------------------------------------|-----|------|-----|------|

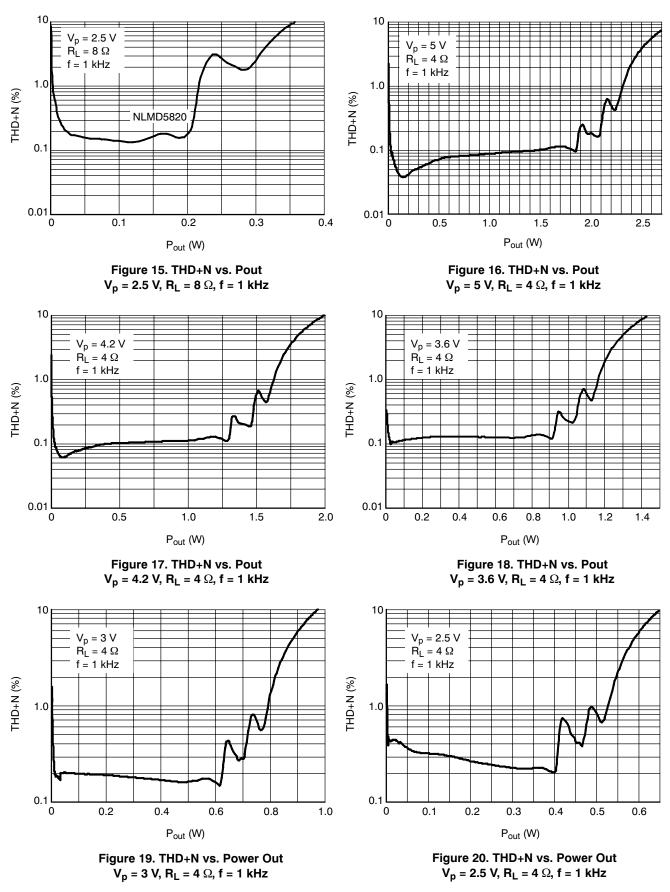

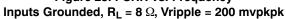

| Total Harmonic Distortion + Noise | THD+N  | V <sub>p</sub> = 5.0 V, R <sub>L</sub> = 8.0 Ω,<br>f = 1.0 kHz, P <sub>out</sub> = 0.25 W | _   | 0.05 | _   | %    |

|                                   |        | $V_{p} = 3.6 \text{ V}, \text{ R}_{L} = 8.0 \Omega,$                                      |     |      |     |      |

|                                   |        | f = 1.0 kHz, P <sub>out</sub> = 0.25 W                                                    | -   | 0.06 | -   |      |

| Common Mode Rejection Ratio       | CMRR   | V <sub>p</sub> from 2.5 V to 5.5 V                                                        |     |      |     | dB   |

|                                   |        | $V_{ic}$ = 0.5 V to $V_p$ – 0.8 V                                                         | -   | -62  | -   |      |

|                                   |        | $V_p = 3.6 V$ , $V_{ic} = 1.0 V_{pp}$                                                     |     |      |     |      |

|                                   |        | f = 217 Hz                                                                                | -   | -56  | -   |      |

|                                   |        | f = 1.0 kHz                                                                               | -   | -57  | -   |      |

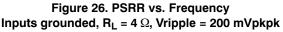

| Power Supply Rejection Ratio      | PSRR   | $V_{p \ ripple \ pk-pk}$ = 200 mV, $R_{L}$ = 8.0 $\Omega$ ,                               |     |      |     | dB   |

|                                   |        | Inputs AC Grounded                                                                        |     |      |     |      |

|                                   |        | V <sub>p</sub> = 3.6 V                                                                    |     |      |     |      |

|                                   |        | f = 217 kHz                                                                               | -   | -62  | -   |      |

|                                   |        | f = 1.0 kHz                                                                               | -   | -65  | -   |      |

### DC ELECTRICAL CHARACTERISTICS OF SWITCHES

| Characteristic                | Symbol               | Conditions                                                      | Min        | Тур          | Max          | Unit            |

|-------------------------------|----------------------|-----------------------------------------------------------------|------------|--------------|--------------|-----------------|

| Control Input High Voltage    | V <sub>IH</sub>      | VCC = 3.0 V<br>VCC = 4.2 V                                      | 1.4<br>2.0 |              |              | V               |

| Control Input Low Voltage     | VIL                  | VCC = 3.0 V<br>VCC = 4.2 V                                      |            |              | 0.7<br>0.8   | V               |

| Control Input Leakage Current | I <sub>IN</sub>      | V <sub>IN</sub> = V <sub>CC</sub> or GND                        |            | ±0.1         | ±1.0         | μΑ              |

| ON State Leakage Current      | I <sub>COM(ON)</sub> | $0 V < V_{COM}, V_{NC} < V_{CC}$                                |            | ±10          | ±100         | nA              |

| OFF State Leakage Current     | I <sub>NC(OFF)</sub> | $0 V < V_{COM}, V_{NC} < V_{CC}$                                |            | ±5           | ±50          | nA              |

| Quiescent Current             | Icc                  | All Channels ON or OFF, $V_{IN} = V_{CC}$ or GND, $I_{OUT} = 0$ |            | ±1.0         | ±2.0         | μΑ              |

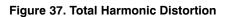

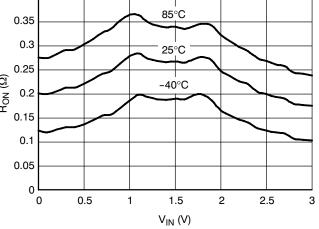

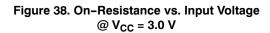

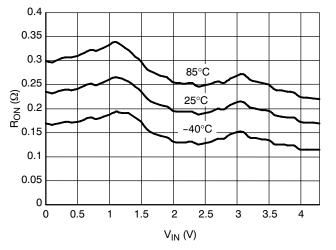

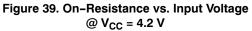

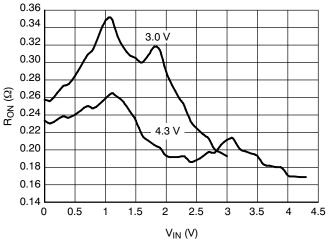

| ON Resistance                 | R <sub>ON</sub>      | VCC = 3.0 V<br>VCC = 4.2 V                                      |            | 0.4<br>0.35  | 0.5<br>0.4   | Ω<br>Ω          |

| R <sub>ON</sub> Flatness      | R <sub>FLAT</sub>    | VCC = 3.0 V<br>VCC = 4.2 V                                      |            | 0.16<br>0.11 | 0.20<br>0.14 | $\Omega \Omega$ |

| R <sub>ON</sub> Matching      | $\Delta R_{ON}$      | VCC = 3.0 V<br>VCC = 4.2 V                                      |            | 0.05<br>0.05 | 0.05<br>0.05 | Ω<br>Ω          |

| Symbol           | Parameter                                                              | Test Conditions                                                                                                                                         | Min | Тур   | Max | Unit |

|------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

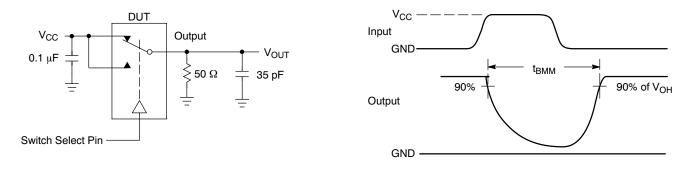

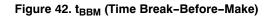

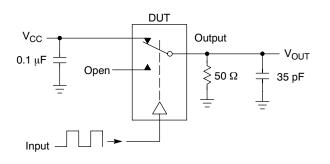

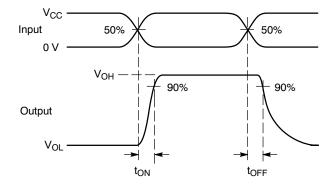

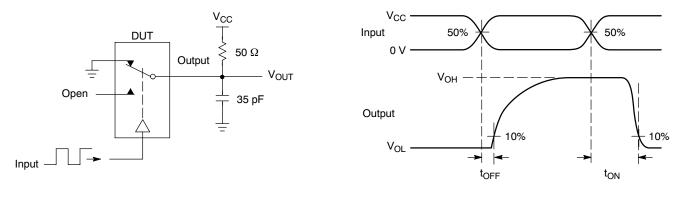

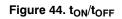

| t <sub>ON</sub>  | Turn-On Time                                                           | $R_L$ = 50 $\Omega,C_L$ = 35 pF (Figures 43 and 44)                                                                                                     |     | 50    |     | ns   |

| t <sub>OFF</sub> | Turn-Off Time                                                          | $\rm R_L$ = 50 $\Omega, \rm C_L$ = 35 pF (Figures 43 and 44)                                                                                            |     | 30    |     | ns   |

| C <sub>IN</sub>  | Control Pin Input Capacitance                                          | V <sub>CC</sub> = 0 V                                                                                                                                   |     | 3.5   |     | pF   |

| C <sub>NC</sub>  | NC Port Capacitance                                                    | $V_{CC} = 3.3 \text{ V}, V_{IN} = 0 \text{ V}$                                                                                                          |     | 60    |     | pF   |

| C <sub>COM</sub> | COM Port Capacitance When Switch is<br>Enabled                         | $V_{CC} = V_{IN} = 3.3 V$                                                                                                                               |     | 200   |     | pF   |

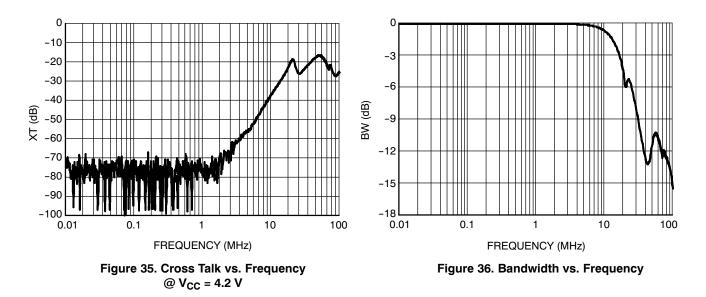

| BW               | Maximum On-Channel -3 dB<br>Bandwidth or Minimum Frequency<br>Response | $V_{\text{IN}}$ centered between $V_{\text{CC}}$ and GND (Figure 45)                                                                                    |     | 19    |     | MHz  |

| V <sub>ONL</sub> | Maximum Feed-through On Loss                                           | $V_{IN}$ = 0 dBm @ 100 kHz to 50 MHz<br>$V_{IN}$ centered between $V_{CC}$ and GND (Figure 45)                                                          |     | -0.06 |     | dB   |

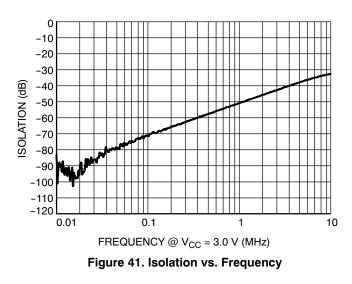

| V <sub>ISO</sub> | Off-Channel Isolation                                                  | f = 100 kHz; $V_{IS}$ = 1 V RMS; $C_L$ = 5.0 pF<br>$V_{IN}$ centered between $V_{CC}$ and GND (Figure 45)                                               |     | -68   |     | dB   |

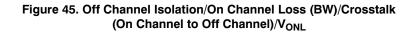

| Q                | Charge Injection Select Input to<br>Common I/O                         | $V_{IN} = V_{CC to}$ GND, $R_{IS} = 0 \Omega$ , $C_L = 1.0 nF$<br>Q = C <sub>L</sub> x DV <sub>OUT</sub> (Figure 46)                                    |     | 38    |     | рC   |

| THD              | Total Harmonic Distortion THD + Noise                                  | ${\sf F}_{\sf IS}$ = 20 Hz to 20 kHz, ${\sf R}_{\sf L}$ = ${\sf R}_{\sf gen}$ = 600 $\Omega,$ ${\sf C}_{\sf L}$ = 50 pF, ${\sf V}_{\sf IS}$ = 2.0 V RMS |     | 0.08  |     | %    |

| VCT              | Channel-to-Channel Crosstalk                                           | f = 100 kHz; $V_{IS}$ = 1.0 V RMS, $C_L$ = 5.0 pF, $R_L$ = 50 $\Omega$ V <sub>IN</sub> centered between V <sub>CC</sub> and GND (Figure 45)             |     | -70   |     | dB   |

### AC ELECTRICAL CHARACTERISTICS OF SWITCHES (Input $t_r = t_f = 3.0 \text{ ns}$ )

## NOTES:

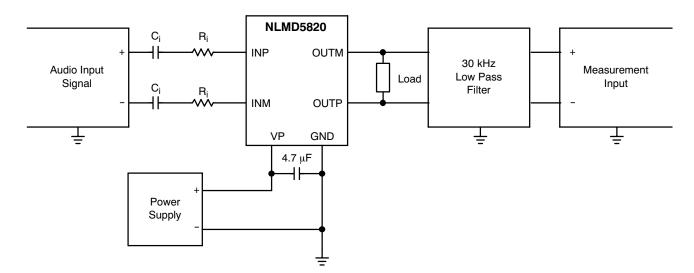

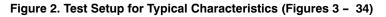

- 1. Unless otherwise noted,  $C_i = 100 \text{ nF}$  and  $R_i = 150 \text{ k}\Omega$ . Thus, the gain setting is 2 V/V and the cutoff frequency of the input high pass filter is set to 10 Hz. Input capacitors are shorted for CMRR measurements.

- 2. To closely reproduce a real application case, all measurements are performed using the following loads:

$R_L = 8 \Omega$  means Load = 15  $\mu$ H + 8  $\Omega$  + 15  $\mu$ H

$R_L = 4 \Omega$  means Load = 15  $\mu$ H + 4  $\Omega$  + 15  $\mu$ H

Very low DCR 15  $\mu$ H inductors (50 m $\Omega$ ) have been used for the following graphs. Thus, the electrical load measurements are performed on the resistor (8  $\Omega$  or 4  $\Omega$ ) in differential mode.

3. For Efficiency measurements, the optional 30 kHz filter is used. An RC low-pass filter is selected with (100  $\Omega$ , 47 nF) on each PWM output.

### **TYPICAL CHARACTERISTICS OF AMPLIFIER**

#### **TYPICAL CHARACTERISTICS OF AMPLIFIER**

## **TYPICAL CHARACTERISTICS OF AMPLIFIER**

**TYPICAL CHARACTERISTICS OF AMPLIFIER**

with 1  $\mu$ F V<sub>p</sub> = 5 V

# **TYPICAL CHARACTERISTICS OF AMPLIFIER**

## **TYPICAL CHARACTERISTICS OF SWITCHES**

# **TYPICAL CHARACTERISTICS OF SWITCHES**

Figure 43. t<sub>ON</sub>/t<sub>OFF</sub>

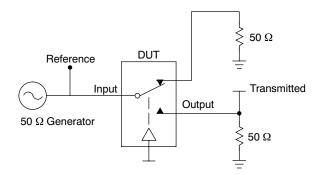

Channel switch control/s test socket is normalized. Off isolation is measured across an off channel. On loss is the bandwidth of an On switch.  $V_{ISO}$ , Bandwidth and  $V_{ONL}$  are independent of the input signal direction.

$$\begin{split} V_{ISO} &= \text{Off Channel Isolation} = 20 \ \text{Log} \Big( \frac{V_{OUT}}{V_{IN}} \Big) \text{for } V_{IN} \text{ at } 100 \ \text{kHz} \\ V_{ONL} &= \text{On Channel Loss} = 20 \ \text{Log} \Big( \frac{V_{OUT}}{V_{IN}} \Big) \text{ for } V_{IN} \text{ at } 100 \ \text{kHz} \text{ to } 50 \ \text{MHz} \end{split}$$

Bandwidth (BW) = the frequency 3 dB below V<sub>ONL</sub> V<sub>CT</sub> = Use V<sub>ISO</sub> setup and test to all other switch analog input/outputs terminated with 50  $\Omega$

Figure 46. Charge Injection: (Q)

### **DESCRIPTION INFORMATION**

#### **Detailed Description**

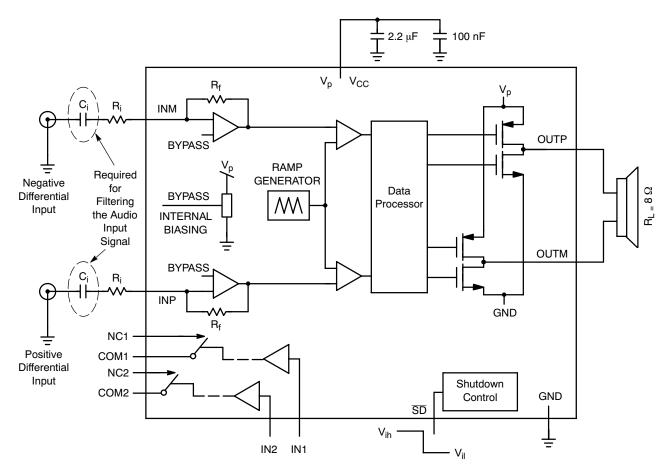

The basic structure of the amplifier portion of the NLMD5820 is composed of one analog pre-amplifier, a pulse width modulator and an H-bridge CMOS power stage. The first stage is externally configurable with gain-setting resistor  $R_i$  and the internal fixed feedback resistor  $R_f$  (the closed-loop gain is fixed by the ratios of these resistors) and the other stage is fixed. The load is driven differentially through two output stages.

The differential PWM output signal is a digital image of the analog audio input signal. The human ear is a band pass filter regarding acoustic waveforms, the typical values of which are 20 Hz and 20 kHz. Thus, the user will hear only the amplified audio input signal within the frequency range. The switching frequency and its harmonics are fully filtered. The inductive parasitic element of the loudspeaker helps to guarantee a superior distortion value.

#### **Power Amplifier**

The output PMOS and NMOS transistors of the amplifier have been designed to deliver the output power of the specifications without clipping. The channel resistance ( $R_{on}$ ) of the NMOS and PMOS transistors is typically 0.4  $\Omega$ .

# Turn On and Turn Off Transitions in Case of 9 Pin Flip-Chip Package

In order to eliminate "pop and click" noises during transition, the output power in the load must not be established or cutoff suddenly. When a logic high is applied to the shutdown pin, the internal biasing voltage rises quickly and, 4 ms later, once the output DC level is around the common mode voltage, the gain is established slowly (5.0 ms). This method to turn on the device is optimized in terms of rejection of "pop and click" noises. Thus, the total turn on time to get full power to the load is 9 ms (typical).

The device has the same behavior when it is turned-off by a logic low on the shutdown pin. No power is delivered to the load 5 ms after a falling edge on the shutdown pin. Due to the fast turn on and off times, the shutdown signal can be used as a mute signal as well.

#### Turn On and Turn Off Transitions in Case of UDFN8

In case of UDFN8 package, the audio signal is established instantaneously after the rising edge on the shutdown pin. The audio is also suddenly cut once a low level is sent to the amplifier. This way to turn on and off the device in a very fast way also prevents from "pop & click" noise.

#### **Shutdown Function**

The device enters shutdown mode when the shutdown signal is low. During the shutdown mode, the DC quiescent current of the circuit does not exceed  $1.5 \ \mu$ A.

#### **Current Breaker Circuit**

The maximum output power of the circuit corresponds to an average current in the load of 820 mA.

In order to limit the excessive power dissipation in the load if a short-circuit occurs, a current breaker cell shuts down the output stage. The current in the four output MOS transistors are real-time controlled, and if one current exceeds the threshold set to 1.5 A, the MOS transistor is opened and the current is reduced to zero. As soon as the short-circuit is removed, the circuit is able to deliver the expected output power.

This patented structure protects the NLMD5820. Since it completely turns off the load, it minimizes the risk of the chip overheating which could occur if a soft current limiting circuit was used.

### **Dual SPST Switch**

The NLMD5820 features an integrated dual SPST analog switch. The control for the switch is operated independently of the amplifier, allowing the audio system a choice between routing signals through the amplifier or letting them pass unaffected through the switch. When the switch is open, it maintains significant off isolation to minimize the effects of the amplifier output on the system.

#### APPLICATION INFORMATION

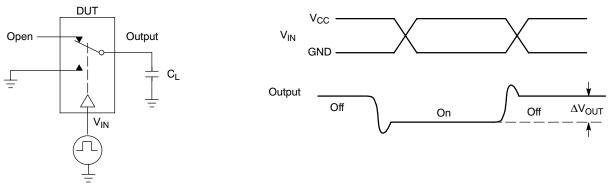

#### NLMD5820 PWM Modulation Scheme

The NLMD5820 uses a PWM modulation scheme with each output switching from 0 to the supply voltage. If  $V_{in} = 0$  V outputs OUTM and OUTP are in phase and no current is flowing through the differential load. When a positive

signal is applied, OUTP duty cycle is greater than 50% and OUTM is less than 50%. With this configuration, the current through the load is 0 A most of the switching period and thus power losses in the load are lowered.

#### Voltage Gain

The first stage is an analog amplifier. The second stage is a comparator: the output of the first stage is compared with a periodic ramp signal. The output comparator gives a pulse width modulation signal (PWM). The third and last stage is the direct conversion of the PWM signal with MOS transistors H-bridge into a powerful output signal with low impedance capability.

With an 8  $\Omega$  load, the total gain of the device is typically set to:

#### Input Capacitor Selection (Cin)

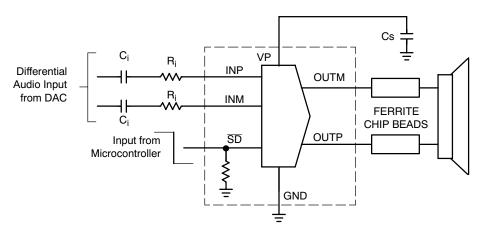

The input coupling capacitor blocks the DC voltage at the amplifier input terminal. This capacitor creates a high-pass filter with R<sub>in</sub>, the cut-off frequency is given by  $Fc = \frac{1}{2 \times \pi \times R_{i} \times C_{i}}.$

When using an input resistor set to 150 k $\Omega$ , the gain configuration is 2 V/V. In such a case, the input capacitor selection can be from 10 nF to 1  $\mu$ F with cutoff frequency values between 1 Hz and 100 Hz. The NLMD5820 also includes a built in low pass filtering function. It's cut off frequency is set to 20 kHz.

#### **Optional Output Filter**

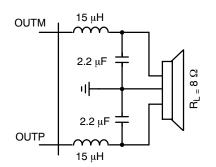

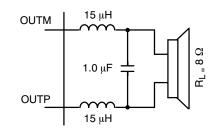

This filter is optional due to the capability of the speaker to filter by itself the high frequency signal. Nevertheless, the high frequency is not audible and filtered by the human ear. An optional filter can be used for filtering high frequency signal before the speaker. In this case, the circuit consists of two inductors (15  $\mu$ H) and two capacitors (2.2  $\mu$ F). The size of the inductors is linked to the output power requested by the application. A simplified version of this filter requires a 1  $\mu$ F capacitor in parallel with the load, instead of two 2.2  $\mu$ F connected to ground).

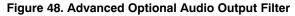

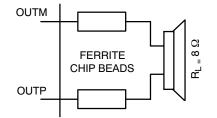

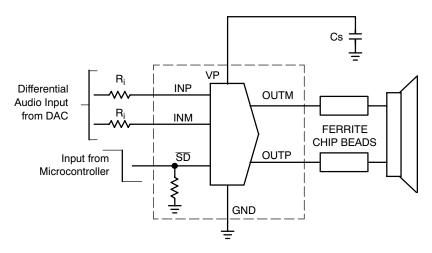

Cellular phones and portable electronic devices are great applications for Filterless Class–D as the track length between the amplifier and the speaker is short, thus, there is usually no need for an EMI filter. However, to lower radiated emissions as much as possible when used in filterless mode, a ferrite filter can often be used. Select a ferrite bead with the high impedance around 100 MHz and a very low DCR value in the audio frequency range is the best choice. The MPZ1608S221A1 from TDK is a good choice. The package size is 0603.

#### **Optimum Equivalent Capacitance at Output Stage**

If the optional filter described in the above section isn't selected. Cellular phones and wireless portable devices design normally put several Radio Frequency filtering capacitors and ESD protection devices between Filter less Class D outputs and loudspeaker. Those devices are usually connected between amplifier output and ground. In order to achieve the best sound quality, the optimum value of total equivalent capacitance between each output terminal to the ground should be less than or equal to 150 pF. This total equivalent capacitance consists of the radio frequency filtering capacitors and ESD protection device equivalent parasitic capacitance.

Figure 49. Optional Audio Output Filter

Figure 50. Optional EMI Ferrite Bead Filter

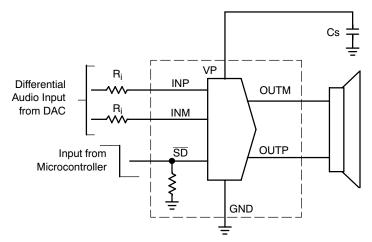

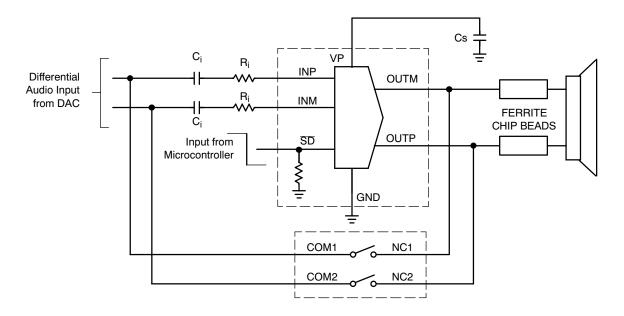

Figure 51. NLMD5820 Application Schematic with Fully Differential Input Configuration

Figure 52. NLMD5820 Application Schematic with Fully Differential Input Configuration and Ferrite Chip Beads as an Output EMI Filter

Figure 53. NLMD5820 Application Schematic with Differential Input Configuration and High Pass Filtering Function

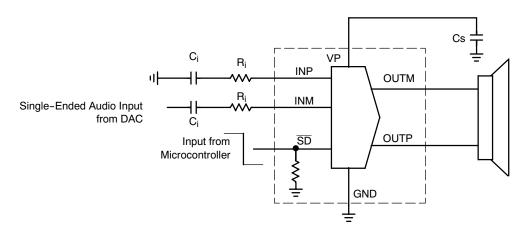

Figure 54. NLMD5820 Application Schematic with Single Ended Input Configuration

Figure 55. NLMD5820 Application Schematic Using Switches as Optional Bypass

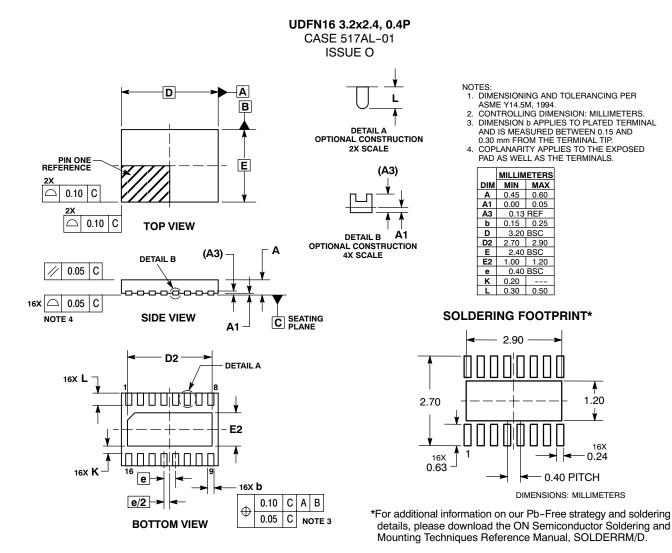

#### PACKAGE DIMENSIONS

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its petent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

#### ON Semiconductor Website: www.onsemi.com

1.20

16X

0.24

Order Literature: http://www.onsemi.com/orderlit

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

For additional information, please contact your local Sales Representative